近日,在第六届国际先进光刻技术研讨会上,佳能公司半导体设备开发部总经理Keita Sake分享了半导体器件制造中纳米压印光刻(NIL)技术的最新进展。

NIL技术是铠侠公司与佳能合作研发的光刻技术。其工作原理是以机械复制品为基础,利用印刷技术和微电子制造技术相结合,采用电子束刻蚀技术,避免了光的衍射。它可以解决光学衍射所带来的分辨率限制,使电子线路宽度更小,理论上,它的分辨率要高于EUV光刻机。

目前,Kioxia已经将NIL技术应用到了15nm NAND闪存器上,并有望在2025年推出应用NIL技术的5nm芯片。

Keita Sake首先介绍了NIL技术的应用空间。NZ2C与模板的结合可以提供多种多样的解决方案,超越摩尔定律是其主要目标,佳能正在尝试将NIL技术应用到DRAM和CPU等逻辑芯片上。

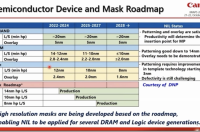

然后,Keita Sake分享了半导体器件和掩膜路线图。在2022年-2024年间3D NAND使用工艺需要套刻精度5nm、DRAM使用设备工艺需要套刻精度2.8-2.4nm、逻辑器件使用设备工艺需要套刻精度2.4nm;在2025-2027年间,3D NAND使用设备工艺需要套刻精度5nm、DRAM使用设备工艺需要套刻精度2.2-2.0nm、逻辑器件使用设备工艺需要套刻精度2nm;在2028之后,3D NAND使用设备工艺需要套刻精度5nm、DRAM使用设备工艺需要小于2nm、逻辑器件使用设备工艺则达到了1.6nm。

Keita Sake表示,基于该路线图,高分辨率掩膜正在开发,使NIL应用于多个DRAM个逻辑设备迭代。

关于NIL技术的套刻精度稳定性方面,Keita Sake表示其系统对XMMO有各种失真校正方法包括磁力闭环控制(CLCM)、高阶畸变矫正(HODC)、跌落模式补偿(DPC)、压印倾斜、精细掩膜等。

针对3D NAND方面,NIL技术的日常套刻精度稳定性,3.5个月内有45个数据点,满足3D NAND大规模生产水平。

针对DRAM方面,佳能一直在不断改进套刻精度。使用POI 控制技术、晶圆区卡盘控制、精细掩膜等方式有助于改善套刻精度。

佳能在缺陷检测方面,使用KLA 2905检测的随机缺陷密度后,进行缺陷复查。结果表明,NIL技术的日常缺陷稳定性满足3D NAND大规模生产水平。

使用不同粒子加法器在几种NIL工具上的测试结果表明,无论何种工具都稳定的保持NIL刀具的清洁度,并且除了提高NIL工具的清洁度外,利用清洁和检查方法也有助于减少颗粒的相关缺陷。如果将晶圆颗粒检测器(WPC)安装在NZ2C工具上,则裸晶片上检测到大于200nm的颗粒。

Keita Sake同时分享了提高生产率的方式。经过实验,设备系统吞吐量与抗蚀剂特性的填充密切相关,在SOC膜存在的情况下,CO2扩散到底层的速度比氦快。模拟结果表明,在抗蚀剂叠层的底层包括SOC膜的情况下,CO2的效率更高。

正因如此,CO2的使用为实现更高的吞吐量提供了一条途径,同时也减少了NIL工具中惰性气体的使用。

在数据管理和系统支持方面,Lithography Plus使用AI方法最大限度的提高设备性能。在佳能公司各部门的配合下,使用大数据搭配合适的曝光工具、光刻工具、计量工具以实现多功能一体系统,提高生产率。

Keita Sake还提到了NIL技术对于环境的影响。佳能根据客户需求提供可持续的NIL技术。为了保持无污染的可持续未来,采用环保工具和工艺,保证低功耗、最小电阻损耗、无抗蚀剂显影过程、无惰性气体,并且适用于设备演进和多样化,其原理简单、无波长或NA分辨率限制,可以制造功耗更低的芯片。

在低功耗方面,预计NIL技术可以作为一种长期制造技术使用,而不会增加功耗,因为即使设备节点在未来进步,图案传输过程本身也不会改变。

最后,Keita Sake进行了总结。高级的NIL工具和掩膜相结合可以为许多不同的应用提供多种解决方案,佳能展示了2.3nm套刻精度应用于各种新技术,主要用在DRAM方面。

*声明:本文系原作者创作。文章内容系其个人观点,我方转载仅为分享与讨论,不代表我方赞成或认同,如有异议,请联系后台。